#### 5.48 Digital Electronics

Tabulate the PLA programmable table for the four Boolean functions listed below.

$$A(x,y,z) = \sum m(0,1,2,4,6)$$

$$B(x,y,z) = \sum m(0,2,6,7)$$

$$C(x,y,z) = \sum m(3,6)$$

$$D(x,y,z) = \sum m(1,3,5,7)$$

Tabulate the PLA programming table for the four Boolean functions listed below. Minimize the number of product terms.

$$A(x,y,z) = \sum (1.2.4.6)$$

$$B(x,y,z) = \sum (0,1.6,7)$$

$$C(x,y,z) = \sum (2,6)$$

$$D(x,y,z) = \sum (1.2,3.5.7)$$

- Derive the PLA programming table for the combinational circuit that squares a 3-bit number. Minimize the number of product terms.

- List the PLA programming table for the BCD to excess 3 code converter whose Boolean functions are simplified.

- List the PAL programming table for the BCD to excess 3 code converter whose Boolean functions are simplified.

- The following is a truth table of a 3-input, 4-output combinational circuit.

Tabulate the PAL programming table for the circuit and mark the fuse map in a PAL diagram.

| I | Inputs |   |   | Out | puts |   |

|---|--------|---|---|-----|------|---|

| x | y      | z | A | B   | C    | D |

| 0 | 0      | 0 | 0 | 1   | 0    | 0 |

| 0 | 0      | 1 | 1 | 1   | 1    | ı |

| 0 | 1      | 0 | 1 | 0   | 1    | 1 |

| 0 | 1      | 1 | 0 | 1   | 0    | 1 |

| 1 | 0      | 0 | 1 | 0   | 1    | 0 |

| 1 | 0      | 1 | 0 | 0   | 0    | 1 |

| 1 | 1      | 0 | 1 | 1   | 1    | 0 |

| 1 | 1      | 1 | 0 | 1   | 1    | 1 |

# Chapter 6

# Synchronous Sequential Logic Circuit

### 6.1 Introduction

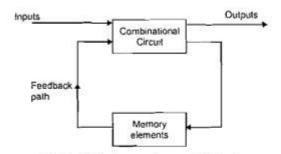

A block diagram of a sequential circuit is shown in Fig. 6.1. It consists of a combinational circuit to which storage elements are connected to form a feedback path. The storage elements are devices capable of storing binary information. This binary information stored in these elements at any given time define the state of the sequential circuit at that time.

Fig 6.1 Block diagram of sequential circuits

The sequential circuit receives the binary information from external inputs. These inputs and the present state of memory elements determine the binary value of the outputs of the circuit. They also determine the condition for changing the state in memory elements. Thus, the next state of the memory elements is also a function of the external inputs and the present state.

# Mealy Model Sequential Circuit

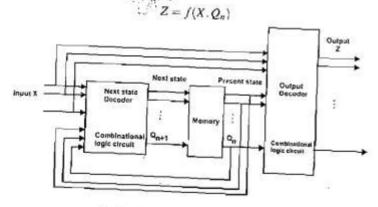

Fig 6.2 shows the clocked synchronous sequential Mealy machine. The output of mealy machine is the function of present inputs and present state (Flip flop outputs). If X is input,  $Q_n$  is the present state and the next state is  $Q_{(n+1)}$ , the output of Mealy function (Z) is given below.

Fig 6.2 Mealy model sequential circuit

The output of memory element is connected to the input of output decoder and next state decoder circuit. The output of memory element is considered as present

# Moore Model Sequential Circuit

Fig 6.3 Moore model sequential circuit

Fig.6.3 shows the block diagram of a Moore machine. The output of Moore machine depends only on the present state. So the output of Moore machine is a function of its present state  $(Q_n)$ . If the input is X, the next state is  $Q_{(n+1)}$  and the p. esent state is  $Q_n$ . The output of Moore machine is represented mathematically

$Z = f(O_n)$

The differences between the Moore machine and Mealy machine are tabulated as follows

| S.No. | Moore machine                                                               | Mealy machine                                                       |

|-------|-----------------------------------------------------------------------------|---------------------------------------------------------------------|

| I.    | The output of this machine is<br>the function of the present state<br>only. | Its output is function of present<br>input as well as present state |

| 2.    | Input changes do not affect the output                                      | Input changes may affect the output of the circuit                  |

| 3.    | It requires more number of states<br>for implementing same function         | It requires less number of states<br>for implementing same function |

# 6.2 Analysis and Synthesis of Synchronous Sequential Circuits

Fig 6.4 Flow chart

### Digital Electronics

The behaviour of sequential circuit can be determined from the inputs, outputs and state of its flip flops. The outputs and next state are both a function of its inputs and the present state. The analysis of a sequential circuit consists of obtaining a state table or state diagram for the time sequence of inputs, outputs and internal states. The analysis of the clocked sequential circuits can be done by following the procedure as shown in Fig.6.4. The reverse process of analysis is known as synthesis of clocked sequential logic circuit.

For the analysis of sequential circuit, we start with the logic diagram. The excitation equation or Boolean expression of each flip-flop is derived from this logic diagram. Then, to obtain the next state equation, we insert the excitation equations into the characteristic equations. The output equations can be derived from the schematic. We can generate the state table using output and next state equations.

# 6.2.1 Analysis of Example Sequential Logic Circuit

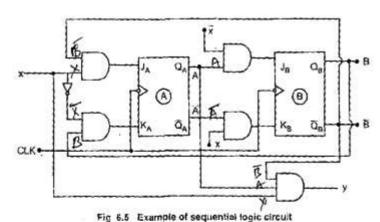

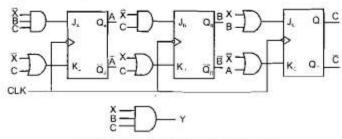

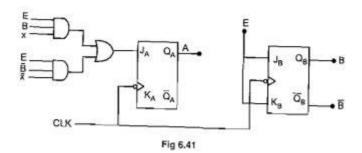

Fig. 6.5 shows a clocked sequential circuit. It has one input variable x, one output variable y and two clocked JK flip flops. The flip flops are labelled as A and B and their outputs are labelled as A and  $\tilde{A}$ . B and  $\tilde{B}$  respectively.

## Step 1: Type of circuit

The output(y) of given logic circuit (Fig.6.5) depends on present input and also on present state (Flip flop outputs) of flip flops, so that the given sequential logic circuit is Mealy sequential machine.

# Step 2: Excitation equations

The excitation equations or Boolean expressions of flip flops A and B are obtained. The equations will be in the form of present states A and B and external input x, since here are two JK flip flops which have output A and B. Therefore the excitation equation (equation formed for flip flop input)

For flip flop - B

For flip flop - B

$$J_A = x\overline{B}$$

$K_A = \overline{x}B$

$J_B = \overline{x}A$

$K_B = x\overline{A}$

Step 3: Next state equations The state equations can be derived directly from the logic diagram. Looking at Fig.6.5 we can see that the signal for J input of the flip flop A is generated by the function  $\widehat{B}_X$  and the signal for input K by the function  $\overrightarrow{B}x$ . Substituting  $J = \overrightarrow{B}x$  and  $K = B\overrightarrow{x}$  into a JK flip flop characteristic equation given by

$$Q_{n+1} = J\overline{Q}_n + \overline{K}Q_n$$

State equation for flip flop A

on for flip flop

$$A$$

$$\overrightarrow{J} = \overrightarrow{K}$$

$$A_{n+1} = (\overrightarrow{B}x)\overrightarrow{Q}_n + (B\overrightarrow{x})Q_n \qquad \text{where } Q_n = A \quad J$$

$$= \overrightarrow{B}x\overrightarrow{A} - \overrightarrow{B}x\overrightarrow{A}$$

$$= \overrightarrow{A}\overrightarrow{B}x + A(\overrightarrow{B}x)$$

$$= \overrightarrow{A}\overrightarrow{B}x + A(\overrightarrow{B} + x)$$

$$= \overrightarrow{A}\overrightarrow{B}x + A\overrightarrow{B} + Ax$$

$$= \overrightarrow{A}\overrightarrow{B} + x(A + \overrightarrow{A}B)$$

$$= AB + x(A + \overrightarrow{B})$$

$$A_{n+1} = A\overrightarrow{B} + Ax + Bx$$

where  $Q_n = A \quad J$

$$(A + \overrightarrow{A}\overrightarrow{B} = A + \overrightarrow{B})$$

$$(A + \overrightarrow{A}\overrightarrow{B} = A + \overrightarrow{B})$$

State equation for flip flop B

Similarly, we can find the state equation for slip slop  $B J = \overline{A}x$  and  $K = \overline{A}x$ . Therefore the state equation of flip flop B is given as

$$B_{n+1} = A\bar{x}\,\bar{B} + (\bar{A}\,\bar{x})B$$

$$= A\bar{x}\bar{B} + (A+\bar{x})B$$

$$= A\bar{x}\bar{B} + AB + B\bar{x}$$

$$= \bar{x}(A\bar{B} + B) + AB$$

$$= \bar{x}(A+B) + AB$$

$$B_{n+1} = A\bar{x} + B\bar{x} + AB$$

### Output equation

The given sequential circuit has output y. The output equation can be found from the Fig.6.5 which is derived using three input AND gate

$$y = A \overline{B} x$$

### Step 4: State table

Table 6.1 is the state table for the given sequential logic circuit. It represents the relationship between input, output and flip flop states. It consists of three columns: present state, next state and output

Present state: It specifies the state of the flip flop before occurrence of a clock pulse.

Next state: It is the state of flip flop after the application of a clock pulse.

Output: This section gives the value of the output variables during the present state. Both next state and output section have two columns representing two possible input conditions x = 0 and x = 1.

Table 6.1

| Present state | Next  | state | Output |       |  |

|---------------|-------|-------|--------|-------|--|

|               | AB    | AB    |        |       |  |

| AB            | x = 0 | x = 1 | x = 0  | x = 1 |  |

| 00            | 00    | 10    | 0      | 0     |  |

| 01            | 01    | 00    | 0      | 0     |  |

| 10            | 11    | 10    | 0      | 1     |  |

| 11            | 01    | 11    | 0      | 1     |  |

We can derive the state table as follows

(i) If present state AB = 00, x = 0

When a present state is 00 i.e. A = 0 and B = 0 and input x = 0, the next state is obtained by using next state equation

Next state for flip flop A

$$A_{n+1} = A\overline{B} + Ax + \overline{B}x$$

$$= 01 + 0.0 + 1.0$$

$$= 0$$

Next state for flip flop B

$$B_{n+1} = A\bar{x} + B\bar{x} + AB$$

= 0.1 + 0.1 + 0.0

= 0

Next state for this case AB = 00

(ii) If present state AB = 00.x = 1

Next state for flip-flop A

$$A_{n+1} = A\overline{B} + Ax + \overline{B}x$$

$$= 0.1 + 0.1 + 1.1$$

$$= 1$$

Next state flip flop B

$$B_{n+1} = A\bar{x} + B\bar{x} + AB$$

= 0.0 + 0.0 + 0.0

= 0

Next state for this case AB = 10

Similarly we can obtain next state for all these different cases as shown in the table.

(iii) Determine the entries in the output section. For this, we have to examine AND gate for all possible present states and input.

(a) If a present state

$$AB = 00$$

,  $x = 0$  output  $y = A\overline{B}x$

$$= 0.10$$

$$y = 0$$

(b) If a present state

$$AB = 00$$

.  $x = 1$

output  $y = A\widetilde{B}x$

$= 0.11$

$y = 0$

Thus, the state table of any sequential circuit can be obtained by the same procedure used in the above example. This example contains 2 flip flops and one input, and one output, producing four rows, two columns in the next state and output sections. In general, a sequential circuit with m flip-flops and n-input variables produces 2" rows and one for each state and 2" columns, one for each input combination in the next state and output sections of the state table.

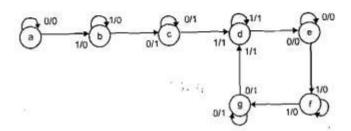

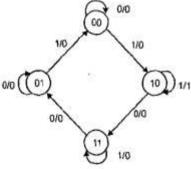

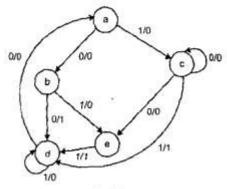

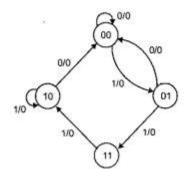

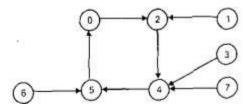

#### Step 5 State diagram

State diagram is a graphical representation of a state table. Fig. 6.6 shows the state diagram for sequential circuit. Here each state is represented by a circle. and transition between states is indicated by directed lines connecting the circles. The binary number inside each circle identifies the state represented by the circle. The directed lines are labelled with two binary numbers separated by a symbol '/' (slash). The input value that causes the state transition is labelled first and output value is next.

Fig 6.6 State diagram of Fig.6.5

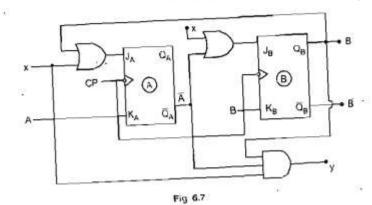

Example 6.1 Derive the state table and state diagram for the sequential circuit shown in Fig.6.7(a).

#### Solution

#### Step 1: Type of circuit

The output y of given sequential circuit (Fig.6.7) depends on the present input and also present state (flip flop output) of flip flops, so the given sequential logic circuit is Mealy sequential machine.

### Step 2: Excitation equation

For flip flop A

$$J_A = x + B$$

$$K_A = A$$

Synchronous Sequential Logic Circuit

For flip flop B

$$J_B = \overline{A} + X$$

$$K_B = B$$

Step 3

We know that characteristic equation of JK flip flop

$$Q_{n+1} = I\overline{Q}_n + \overline{K}Q_n$$

State equation for flip flop A

$$A_{n+1} = (x+B)\overline{Q}_n + AQ_n \qquad \text{(where } Q_n = A \text{ for flip flop } A)$$

$$= (x+B)\overline{A} + \overline{A}A$$

$$= \overline{A}x + \overline{A}B + 0$$

$$A_{n+1} = \overline{A}x + \overline{A}B$$

State equation for flip flop B

$$B_{n+1} = (\overline{A} + x)\overline{Q}_n + \overline{B}Q_n$$

(where  $Q_n = B$  for flip flop  $B$ )

$$= (\overline{A} + x)\overline{B} + \overline{B}B$$

$$B_{n+1} = \overline{A} \ \overline{B} + \overline{B}x$$

Output equation

$$v \leftarrow \overline{A}Bx$$

# Step 4 : State table

| Present state | Next  | state | Output |       |  |

|---------------|-------|-------|--------|-------|--|

|               | AB    | AB    | Output |       |  |

| AB            | x = 0 | v = 1 |        | y     |  |

| 00            | 00    | 71    | x = 0  | x = 1 |  |

| 01            | 10    | - 10  | _0_    | 0     |  |

| 10            | 01    | 10    | 0      | T     |  |

| 11            | -01   | 00    | 0      | 0     |  |

|               | 00    | 00    | 0      | 0     |  |

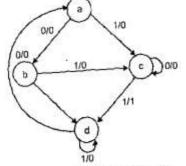

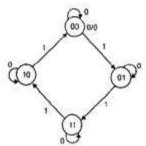

# Step 5 : State diagram

Fig 6.8

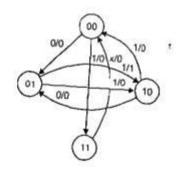

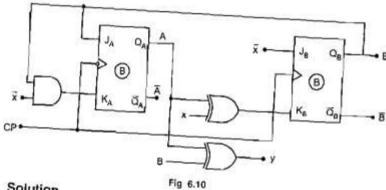

Example 6.2 Derive the state table and state diagram for the sequential circuit

## Solution

# Step 1 : Type of circuit

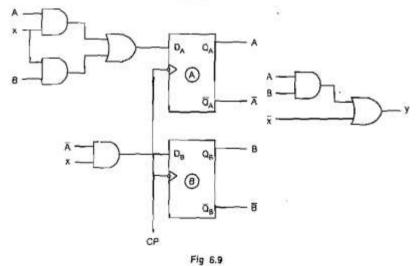

The output of a given circuit(See Fig.6.9) depends on present input and also on present states, so the given sequential logic circuit is Mealy machines

# Step 2: Excitation Equation

For flip flop A  $D_A = A_X + B_X$ For Flip flip B  $D_R = \overline{A}_X$ For Output  $y = AB + \overline{x}$

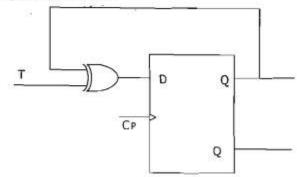

# Step 3: We know that characteristic equation of D flip flop (next state depends on input

Step 4: State table

The state table contains four rows and three columns. The next state and output have two sub columns.

| Present state | Next  | state | Output |       |  |

|---------------|-------|-------|--------|-------|--|

|               | AB    | AB    |        |       |  |

| AB            | x = 0 | x = 1 | x = 0  | x = 1 |  |

| 00            | 00    | 10    | 0      | 0     |  |

| 01            | 00    | -11   | 1      | 0     |  |

| 10            | 00    | 10    | 1      | 0     |  |

| 11            | 00    | 10    | 1      | 0     |  |

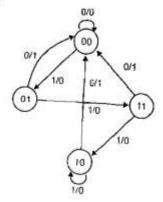

# Step 5: State Diagram

Example 6.3 Derive the state table and state diagram for sequential circuit

## Solution

# Step 1: Type of circuit

The output y of the sequential circuit depends on present state only, so the given logic circuit is the Moore type circuit. Step 2: Excitation equations

For flip flop

$$A$$

$$J_A = B$$

$$K_A = B\bar{x}$$

For flip flop  $B$

$$J_B = \bar{x}$$

$$K_B = A \oplus x$$

$$y = A \oplus B$$

#### Step 3:

We know that characteristics equation of JK flip flop

$$A_{n+1} = J\overline{Q}_n + \overline{K}Q_n$$

State equation for flip flop  $A: A_{n+1} = B\overline{A} + (\overline{B}\overline{x}) A$  (:  $Q_n = A$ )

$$= B\overline{A} + A(\overline{B} + x)$$

$$= B\overline{A} + A\overline{B} + x$$

$$A_{n-1} = (A \oplus B) + x$$

State equation for flip flop  $B: B_{n+1} = \overline{x}\overline{B} + (\overline{A} \oplus x)B$

$$= \overline{x} \overline{B} + (Ax + \overline{A} \overline{x})B$$

$$B_{n+1} = \overline{x}\overline{B} + AxB + \overline{A}\overline{x}B$$

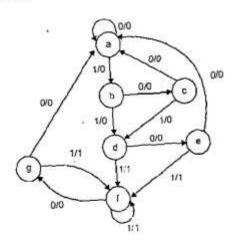

#### Step 4: State table

| Present state | Next  | Output |     |  |

|---------------|-------|--------|-----|--|

|               | x = 0 | x = 1  | у   |  |

| AB            | AB    | AB     | 8 8 |  |

| 00            | 01    | 00     | 0   |  |

| 01            | 11    | 10     | Ti- |  |

| 10            | 11    | 10     | 1   |  |

| 11            | 00    | 11     | 0   |  |

#### State diagram

Note: The state diagram for Moore machine is different from Mealy machine. Here each circle is coded with state binary number/output.

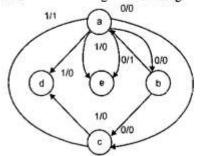

### 6.3 State Reduction

Any logic design process must consider the problem of minimizing the cost of the final circuit. One way to reduce the cost is by reducing the number of flip flops, i.e. by reducing the number of states. The state reduction technique basically avoids the introduction of redundant equivalent states. The reduction of redundant states reduces the number of flip flops and logic gates required, thus reducing the cost of the tinal circuit. Two states are said to be redundant or equivalent, if every possible set of inputs generate exactly the same outputs and the same next states. When two states are equivalent, one of them can be removed without altering input-output relationship. Let us consider the state diagram shown in Fig 6.11. The states are denoted by letter symbols instead of their binary values because in state reduction technique internal states are also important, but input output sequences are more Important. The procedure contains two steps.

Step 1: Finding the state table for the given state diagram

First the given state diagram is converted into a state table. Fig.6.11 shows the example of state diagram.

| Present state | Next | Next state |     | out  |                   |

|---------------|------|------------|-----|------|-------------------|

|               | x=0  | X=1        | x=0 | x=1  |                   |

| а             | Ь    | c          | 0   | 0    | Both are          |

| b             | d    | e          | 1   | 0    | equivalent states |

| · c           | C    | ď          | 0   | 1 1  | because of state  |

| d             | a    | ď          | 0   | 0    | c and e having    |

| νe            | c    | ď          | 0   | 1.12 | and same cutput   |

Step 2: Finding equivalent states

The two present states go to the same next state and have the same output for both the input combinations. We can easily find this from the state table, states

c and e are equivalent. This is because both c and e states go to states c and d outputs of 0 and 1 for x = 0, x = 1 respectively. Therefore, the state e can be removed and replaced by c. The final reduced table and state diagram are given in the table 6.2 and Fig.6.12. The second row have e state for the input x = 1, it replaced by c because the states c and e are equivalent.

Table 6.2 Reduced state table

| Present | Next  | state | Output |               |  |

|---------|-------|-------|--------|---------------|--|

| state   | AB    | AB    |        |               |  |

| AB      | 0 = x | x = 1 | x = 0  | $\frac{0}{0}$ |  |

| a       | 1     | C     | 1      | o             |  |

| Ь       | d     | 6     | 0      | 1             |  |

| C       | C     | 1 4   | 0      | 0             |  |

| d       | a     | a     | 1      | -             |  |

Fig. 6.12 Reduced state diagram

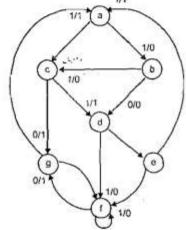

Example 6.4 Obtain the reduced state table and reduced state diagram for a sequential circuit whose state diagram is shown in Fig. 6.13.

Fig 6.13

#### Solution

The given diagram has seven states, one input and one output. As per the step 1, the given state diagram is converted to a state table.

#### State table

Table 6.4(a)

| Present state | Next state |     | Out | out   |

|---------------|------------|-----|-----|-------|

|               | x=0        | x=1 | x=0 | 1 x=1 |

| a             | a<br>c     | b   | 0   | 0     |

| ь             | C          | d   | 0   | l ŏ l |

| c             | a          | d   | 0   | 0     |

|               | e          | !   | . 0 | 1 1   |

|               |            |     | . 0 | i . ← |

|               | 9          |     | 0.  | 1     |

| ********      |            |     | . 0 | 10.4  |

loth are equivalent states ecause of state and g having ame next state and same output

From the above state table, it is clear that states e and g are equivalent. So the state g is replaced by state e. The reduced state table is shown in Ex.6.4

# Reduced state Table

Table 6.4(b)

|                     | Present state | Next  | state | Ou    | tput  |

|---------------------|---------------|-------|-------|-------|-------|

|                     |               | x = 0 | x = 1 | x = 0 | x = 1 |

|                     | a             | а     | Ь     | 0     | 0     |

|                     | b             | c     | d     | 0     | 0     |

|                     | C             | a     | d     | 0     | 0     |

| Both are equivalent | d             | e     | f     | 0     | 1     |

| states              | е .           | а     | f     | 0     | 1     |

|                     | ·             | "     | f     | 0     | Ť     |

From the above reduced table, states d and f are equivalent, hence 'f' can be replaced by d and it can be removed. Then finally the reduced state table is shown

# Final reduced table

The state diagram of the reduced state Table is shown in Fig.6.4(b).

| Present state | Next  | state | Output $x = 0$ $x = 1$ |     |  |

|---------------|-------|-------|------------------------|-----|--|

|               | AB    | AB    |                        |     |  |

| AB            | x = 0 | x = 1 |                        |     |  |

| u             | . 0   | b     | 11                     | ()  |  |

| b             | e.    | d     | 0                      | - 0 |  |

| 1.            | a     | d     | .0                     | 0   |  |

| d             | e.    | d     | ()                     | 1   |  |

| A*            | n     | d     | 0                      | 1   |  |

# State Assignment

In sequential circuits we know that the behaviour of the circuit is defined in terms of its inputs, present state, next state and outputs. To generate the desired next state at particular present state and inputs, it is necessary to have specific flip flop inputs. These flip flop inputs are described by a set of Boolean functions called flip flop input functions. To determine the flip flop input functions, it is necessary to represent states in the state diagram using binary values instead of alphabets. This procedure is known as state assignment. The following rules are used in state assignment.

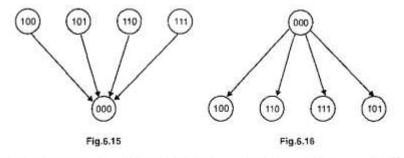

Rule 1. States having the same next states for a given input condition should have assignments which can be grouped into logically adjacent cells in a K-map. (Fig.6.15)

Rule 2. States having different next states should have assignment which can be grouped into logically adjacent cells in K-map. (Fig.6.16)

Example 6.5 Design a sequential circuit using D flip flop for a state diagram given below. Use state assignment rules for assigning states and compare the required combinational circuit with random state

Fig 6.17

#### Solution

The states are a, b, c, d and e. Each state is randomly assigned.

$a=000,\ b=001,\ c=010,\ d=011,\ e=100.$  The remaining combinations are considered as don't care conditions.

### **Excitation table**

|   | The state of the s | t state | Input | N         | ext Sta   | te               | Output |

|---|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|-------|-----------|-----------|------------------|--------|

| A | B                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | C       | X     | $A_{n+1}$ | $B_{n-1}$ | C <sub>n+1</sub> | Z      |

| 0 | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 0       | 0     | 0         | 0         | 1                | -      |

| 0 | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 0 .     | · · I | 0         | 1         | 0                | 0      |

| 0 | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1       | 0     | 0         | 1         | - 1              | 0      |

| 0 | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1       | 1     | 1         | 0         | 0                | 0      |

| 0 | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 0       | 0     | iii       | 0         | 0                | 0      |

| 0 | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 0       | 1     | 0         | 1         | - 0              | 0      |

| 0 | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         | 0     | 0         | 0         | 0                | 0      |

| 0 | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1       | 1     | 0         | 0         | -                | 0      |

| 1 | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 0       | 0     | 0         | 0         | 0                | - 1    |

| 1 | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 0       |       | 0         |           | 0                | t      |

| - |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |       | U         | 0 1       | 0                | 0      |

| Present state |   | Input | Ne | Next State |   | Output |   |

|---------------|---|-------|----|------------|---|--------|---|

| 1             | 0 | 1     | 0  | X          | X | X      | X |

| 1             | 0 | 1     | 1  | X          | X | X      | X |

| 1             | 1 | 0     | 0  | X          | X | X      | X |

| i             | 1 | 0     | 1  | X          | X | X      | X |

| 1             | 1 | 1     | 0  | X          | X | X      | X |

| i             | 1 | 1     | 1  | X          | X | X      | X |

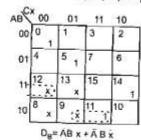

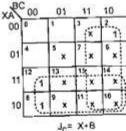

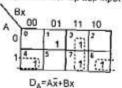

#### K-map simplification

The D flip flop input is equal to next state and the flip flop expression is obtained directly.

Expression for hip flop input Dp

Expression for flip flop input Do

$D_C = \overline{A} \overline{B} \overline{x} + B \overline{C} x$

Expression for flip flop input DD

The random assignment requires

7 three input AND gates

I two input AND gates

4 two input OR gates

Total 12 gates with 31 inputs and 3 flip flops are required to construct the sequential logic circuit. Now we apply state assignment rules, then follow the above steps. 10

From Rule 1, The states e and d must be adjacent

From Rule 2, states b and c must be adjacent. We form the adjacent cells in the 3 variable K-map

| A | 00 | 01       | 11       | 10 |

|---|----|----------|----------|----|

| 0 | 0  | 1<br>(b) | 3.0      | 2  |

| 1 | 4  | 5<br>;à· | 7.<br>e. | 6  |

#### Excitation table

| Present state       | 10.1-1.0-4.4 |            | Next St     | ate      | Output |

|---------------------|--------------|------------|-------------|----------|--------|

| A B C               | . X          | Anti       | $B_{n+1}$   | C,,,!    | Z      |

| 0 0 0               | ···i'···i    | Ö          | 1-7-        |          | 0      |

| 0 0 1               | 0            | 1          | 0           | 1        | 0      |

| 0 1 0               |              | - <u>l</u> | <u>1</u>    | 1        | 0      |

| 0 1 0               | · · i · · ·  | ·x         | ⊹- <u>^</u> | <u>X</u> | X      |

| 0 1 1               | 0            | 1          | 1           | 1        | 0      |

| 1 0 0               | 0            | <br>X      | 0<br>X      |          | 0      |

| 1 0 0               | 1            | X          | · · · · ·   | ··· x    |        |

| 1 0 1               | . 0          | 0          | 0           | 0        | 0      |

| 1 1 0               | 0            | ý          | <u>v</u>    | <u>0</u> | 1<br>X |

| 1 1 0               | 111          | X          | X           | · x      | ··· x  |

| 1444                |              | 0          | 0           | . 0      |        |

| Acceler Commerces . |              |            |             | 0        | 0      |

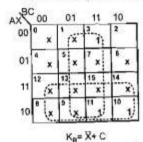

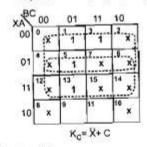

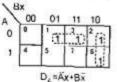

## K- Map simplification

Expression for hip hop input D.

Expression for hip hop input Da

Expression for tip f.op input Do

Expression for  $f_{iip}$   $f_{iop}$  input  $D_{g_i}$

Under the state assignment rules, we require

4 three input AND gates

I two input AND gate

2 two input OR gates

A total of 7 gates with 18 inputs and 3 flip flops are required to construct the sequential logic circuit based on the state assignment rules.

# 6.5 Design Frocedure

The following steps are followed to design the clocked sequential logic circuit.

- Obtain the state table from the given circuit information such as a state diagram, a timing diagram or description.

- 2. The number of states may be reduced by state reduction technique.

- 3. Assign binary values to each state in the state table.

- Determine the number of flip flops required and assign a letter symbol to each flip flop.

- 5. Choose the flip flop type to be used according to the application.

- Derive the excitation table from the reduced state table.

- 7 Derive the expression for flip flop inputs and outputs using k-map simplification (The present state and inputs are considered for k-map simplification) and draw logic circuit using flip flops and gates

# 6.6 Synthesis of Clocked Sequential Logic Circuits

Synthesis means that, it is the reverse process of analysing a sequential logic circuit. In this synthesis, we get a logic circuit from the information of state diagram, word description etc. The detailed steps are given in the example. Now we will see the detailed description of each step.

A state diagram is obtained from the word description, timing diagram or other pertinent information. From this state diagram, we can form a state table.

The reduction of number of states and binary value assignment to each state gives the reduction in combinational circuit requirement. The number of flip flops required to design any sequential logic circuit depends on the number of states.

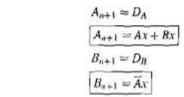

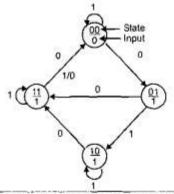

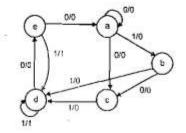

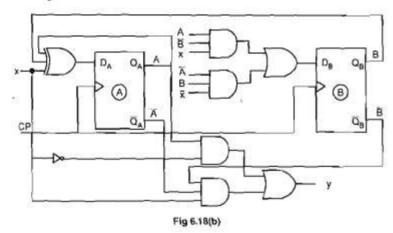

Example 6.6 A sequential circuit has one input and one output and its state diagram is shown in Fig.6.18(a). Design the sequential circuit using D flip flop

Fig 6.18(a)

#### Solution

The given state diagram consists of four states. It has one input (x) and one output (y). The state table for the given state diagram is shown in Table.6.6(a). It is clear that there are no equivalent states. Therefore, there is no reduction in the state diagram. As the state diagram contains 4-states, it requires 2 flip-flops which are named as A and B.

| Present state | Next  | state | Output |        |  |

|---------------|-------|-------|--------|--------|--|

|               | x = 0 | x = 1 | x = 0  | X == 1 |  |

| AB            | AB    | AB    | v      | ν      |  |

| 00            | 00    | 10    | 0      | Í      |  |

| 01            | - 11  | 00    | 0      | 0      |  |

| 10            | 10    | 01    | 1      | 0      |  |

| 11            | 00    | 10    | 1      | 0      |  |

#### Design using D-flip flop

. For the design of circuit using D flip flop (or any flip flop), we need the excitation table. Table Ex 6.6(b) shows the excitation table of D flip flop from which we can develop excitation table for the required circuit as shown in table 6.6(c).

Table 6.6 (b) Excitation table for D-flip flop

| Present state  | Next state | Flip flop input |  |  |

|----------------|------------|-----------------|--|--|

| Q <sub>n</sub> | $Q_{n+1}$  | D               |  |  |

| 0              | 0          | 0               |  |  |

| 0              | 1          | 1               |  |  |

| 1              | 0          | 0               |  |  |

| 1              | ı          | 1               |  |  |

Understan table

| Pres | ent state | Input |   | t state |                | dap input | Output |  |

|------|-----------|-------|---|---------|----------------|-----------|--------|--|

| A    | В         | X     | A | В       | D <sub>A</sub> | $D_B$     | у      |  |

| 0    | 0         | 0     | 0 | 0       | 0              | 0         | 0      |  |

| 0    | 0         | 1     | 1 | 0       | 1              | 0         | 1      |  |

| 0    | 1         | 0     | 1 | 1       | 1              | . 1       | 0      |  |

| O    | 1         | 1     | 0 | 0       | 0              | 0         | 0      |  |

| 1    | 0         | 0     | 1 | 0       | 1              | 0         | 1      |  |

| 1    | 0         | T     | 0 | 1       | 0              | 1         | 0      |  |

| 1    | 1         | 0     | 0 | 0       | 0              | 0         | 1      |  |

| 1    | 1         | 1     | 1 | 0       | 1              | 0         | 0      |  |

The flip-flop input function and the circuit output function are obtained by using K-map simplification.

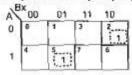

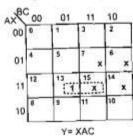

Input equation (or) function for flip flop  $A(D_A)$

| 00 | 14  | 12  | 10  |

|----|-----|-----|-----|

|    | 100 | 3   | 7:  |

|    | 111 | 1 - | 1.1 |

| 4  | 5   | 7   | 6   |

$$D_A = \overrightarrow{A} \overrightarrow{B} x + \overrightarrow{A} \overrightarrow{B} \overrightarrow{x} + A \overrightarrow{B} \overrightarrow{x} + A B x$$

=  $\overrightarrow{A} (\overrightarrow{B} x + B \overrightarrow{x}) + A (\overrightarrow{B} \overrightarrow{x} + B x)$

Let us consider  $z = Bx + B\bar{x}$ , then  $B\bar{x} + Bx = \bar{z}$ . Simplify the above equation

$$DA = \tilde{A}z + A\tilde{z}$$

$$= A \pm i z$$

Substitute  $z = \overline{B}x + B\overline{x} = B + x$  in the above equation

$$D_A = A \oplus B \oplus x$$

Input equation for flip flop  $B(D_R)$

$$D_B = \overline{A}B\overline{x} + A\overline{B}x$$

$$y = Ax + ABx$$

The input equation for flip and output equation are simulated as follows

$$DA = A \oplus B \oplus x$$

$$DB = \overrightarrow{A} B\overrightarrow{x} + A\overrightarrow{B}x$$

$$y = A\overrightarrow{x} + \overrightarrow{A}Bx$$

A sequential circuit using D flip flop is obtained by using the above equations as shown in fig 6.18(b).

# Sequence Generator

A sequential circuit which generates a prescribed sequence of bits, synchronous with the clock, is referred to as a sequence generator. We can construct sequence generators by two ways

- 1. Sequence generators using counters

- Sequence generators using shift registers

# 6.7.1 Sequence Generator using Counters

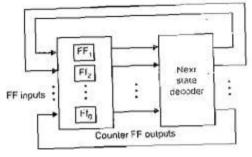

Fig.6.19 shows the block diagram of a sequence generator using counters. It contains two stages

- 1. counter, and

- 2. next state decoder.

Fig 6.19

### **Design Procedure**

Step 1: Determine the number of flip-flops required

The number of flip-flops required to generate a particular sequence can be determined as follows.

- (a) Find the number of 1's in the sequence.

- (b) Find the number of 0's in the sequence.

- (c) Take the maximum value from both. If 'n' is the required number of flip-flops, choose minimum value of 'n' to satisfy the following condition.

$$\max(0's, 1's) \le 2^{n-1}$$

#### Step 2: State assignment

Once the number of flip-flops is decided, we have to assign unique states corresponding to each bit in the given sequence such that the flip-flop representing least significant bit generates the given sequence (the output of the flip-flop which represents the least significant bit is used to represent the given sequence)

- Step 3: Draw the state diagram from the above state assignment and obtain the excitation table from the state diagram.

- Step 4: Find the Boolean expression for each flip-flop input by using k-filap and draw the logic diagram for this Boolean expression

Example 6.7 Find the number of flip-flops required to generate the sequence 10110110.

#### [] Solution

In the given sequence, the number of 0's are 3 and number of 1's are 5.

$$\max (3,5) \le 2^{n-1}$$

$$5 \le 2^n$$

$$\boxed{n=4}$$

Example 6.8 Design a sequence generator using JK flip-flop to generate the sequence 1101011.

#### Solution

#### Step 1: Number of flip-flops required

Number of 0's in the sequence = 2

Number of 1's in the sequence = 5

Hence

$$\max(2,5) \le 2^{n-1}$$

$$5 \le 2^{n-1}$$

$$n = 4$$

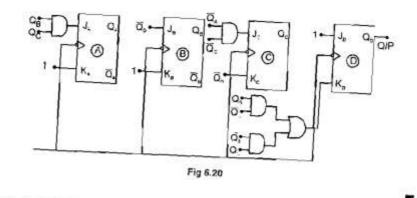

We need four flip-flops named as A, B, C and D. The desired sequence is generated by the D flip-flops output

### Step 2: State assignment

| Decimal<br>equivalent | A | В | С | D   |                            |

|-----------------------|---|---|---|-----|----------------------------|

| 1                     | 0 | 0 | 0 | :14 | — Given sequence           |

| 3                     | 0 | 0 | 1 | 1   | first enter<br>this column |

| 0                     | 0 | 0 | 0 | 0:  | this colonial              |

| 5                     | 0 | 1 | 0 | 11  |                            |

| 2                     | 0 | 0 | 1 | :0: |                            |

| 7                     | 0 | 1 | 1 | 11  |                            |

| 9                     | 1 | 0 | 0 | 11  |                            |

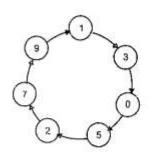

#### Step 3: State diagram

#### **Excitation table**

|       | Preser | it state | 2   |       | Next | state |    |    |    | F     | lip-flo | p inp | uts |       |    |

|-------|--------|----------|-----|-------|------|-------|----|----|----|-------|---------|-------|-----|-------|----|

| $Q_A$ | QB     | Qc       | Qn  | $Q_A$ | Qn   | Qc    | Qn | JA | KA | $J_B$ | KB      | Jc    | Kc  | $J_D$ | Kn |

| 0     | 0      | 0        | 0   | 0     | 1    | 0     | 1  | 0  | X  | 1     | X       | X     | -1  | 1     | X  |

| 0     | 0      | 0        | 1   | 0     | 0    | 1     | 1  | 0  | X  | 0:    | X       | 1     | X   | X     | 0  |

| 0     | 0      | 1        | 0   | 0     | 1    | 1     | 1  | 0  | Х  | 1     | X       | X     | 0   | 1     | X  |

| 0     | 0      | 1        | 1   | 0     | 0    | 0     | 0  | 0  | X  | 0     | X       | X     | 1   | X     | 1  |

| 0     | 1      | 0        | 0   | X     | X    | X     | X  | X  | X  | X     | X       | Х     | X   | X     | X  |

| 0     | 1      | 0        | - 1 | 0     | Ü    | 1     | 0  | 0  | X  | X     | 1       | 1     | X   | X     | 1  |

| 0     | -1     | 1        | 0   | X     | X    | X     | X  | X  | X  | X     | X       | X     | X   | X     | X  |

| 0     | 1      | 1        | 1   | -1    | 0    | 0     | 1  | 13 | X  | X     | - 1     | Х     | 1   | X     | 0  |

| 1     | 0      | 0        | 0   | X     | X    | X     | X  | Х  | X  | X     | X       | X     | Х   | X     | X  |

| 1     | 0      | 0        | 1   | 0     | 0    | 0     | 1  | X  | 1  | 0     | Х       | 0     | X   | X     | 0  |

| 1     | -0     | 1        | 0   | X     | X    | X     | X  | X  | X  | X     | X       | X     | X   | X     | X  |

| 1     | 0      | 1        | - 1 | X     | X    | X     | X  | X  | X  | X     | X       | X     | X   | X     | X  |

| 1     | . 1    | 0        | 0   | X     | X    | X     | X  | X  | X  | X     | X       | X     | X   | X     | X  |

| 1     | 1      | 0        | 1   | X     | X    | X     | X  | X  | X  | X     | X       | X     | X   | X     | X  |

| 1     | 1      | 1        | 0   | X     | X    | X     | X  | X  | X  | X     | X       | X     | X   | X     | X  |

| 1     | 1      | 1        | 1   | X     | X    | X     | X  | X  | X  | X     | X       | X     | X   | X     | X  |

Note: The unused states 4, 6, 8, 10, 11, 12, 13, 14, and 15 are considered as X

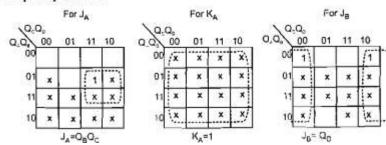

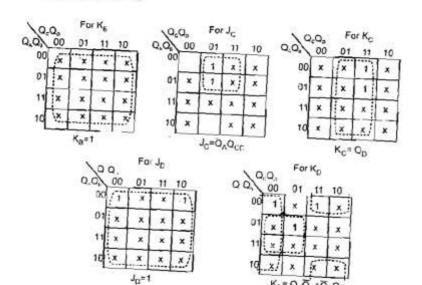

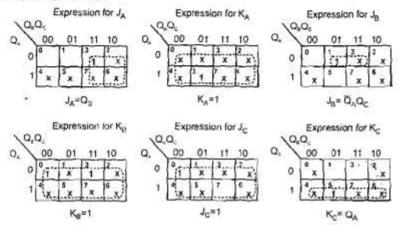

### K-map simplification

# Logic diagram

A CONTRACTOR OF THE PROPERTY O

Example 6.9 Design a pulse train generator for the waveform shown below.

#### □ Solution

Step 1: The pulse is repeated for every 4-bit sequence 0111. Therefore the required number of flip flop is determined as follows.

- (i) number of 0's ≈ 1

- (ii) number of 1's  $\approx 3$

Hence

$$\max (1,3) \le 2^{n-1}$$

$$3 \le 2^{n-1}$$

$$[n=3]$$

We need three flip-flop named as A.B and C. The desired sequence is generated by the C flip-flop.

Step 2: State assignment

| Decimal equivalent | A | В | C |

|--------------------|---|---|---|

| 0                  | 0 | 0 | 0 |

| 1                  | 0 | 0 | 1 |

| 3                  | 0 | 1 | 1 |

| 5                  | 1 | 0 | 1 |

Note: The unused states are 2.4,6 and 7. Consider the don't care (X) for these states in the K-map simplification.

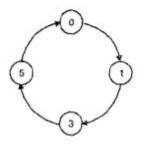

Step 3: State diagram

#### **Excitation table**

| Pre   | sent s   | tate | N   | Next state |    |     | Flip-flop inputs |    |    |    |    |  |  |

|-------|----------|------|-----|------------|----|-----|------------------|----|----|----|----|--|--|

| $Q_A$ | $Q_{li}$ | Qc   | 0,1 | Qy         | Qc | Jy  | K <sub>3</sub>   | JR | KB | 1c | Ke |  |  |

| 0     | 0        | 0    | 0   | 0          | 1  | . 0 | X                | 0  | X  | 1  | X  |  |  |

| 0     | ()       | 1    | 0   | 1          |    | U   | X                | 1  | X  | X  | () |  |  |

| 1)    | 1        | 1    | 1   | 0          | 1  | 1   | X                | X  | 1  | X  | 0  |  |  |

| 1     | 0        | 1    | 0   | 0          | 0  | N   | 71               | 0  | X  | X  | 1  |  |  |

Note: Unused states 2, 4, 6 and 7 are considered as X

15

# Synchronous Sequential Logic Circuit 6.31

#### K-map simplification

This minimal expression form is K-map simplification

$$J_A = Q_B$$

$J_B = \overleftrightarrow{Q}_A Q_C$   $J_C \approx I$

$K_A = I$   $K_B = I$   $K_C = Q_A$

#### Logic diagram

# 6.7.2 Sequence Generator using Shift Registers

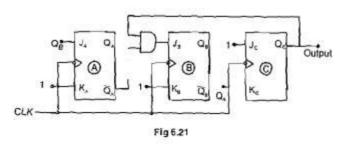

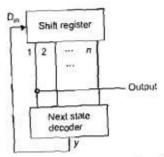

This is another method for designing sequence generator. In this method shift registers with next state decoder logic are used. Fig.6.22 shows the block diagram of sequence generator using shift registers.

From this Fig.6.22, we see that the output of next state decoder is a function of  $Q_A$ ,  $Q_B$ , ...,  $Q_B$ . The next state decoder is a logic circuit which decodes the output of shift register and generates (input to get desired sequence from flip flop A (least significant bit).

Fig 6.22 Block diagram of a sequence generator using shift registers

Example 6.10 Design a sequence generator to generate the sequence 1101011 by shift register method.

In this approach, the minimum number of flip-flops n, required to generate a sequence of length N is given by

$$N \leq 2^{n-1}$$

In this example N = 7 and therefore, the minimum value of n, which may generate the sequence is

$$7 \le 2^n - 1$$

$$\boxed{n = 3}$$

With the three flip-flops, the sequence generation is shown in Table 6.7 The state diagram is shown In Fig.6.23

|                |       | state assi<br>utputs | Din | States |  |

|----------------|-------|----------------------|-----|--------|--|

| Q <sub>A</sub> | $Q_B$ | Qc                   |     | _      |  |

| ĭ              | 0     | 0                    | 1   | 4      |  |

| î              | 0     | 1                    | 0   | 5      |  |

| 0              | 0     | 0                    | 1   | 0      |  |

| ï              | 1     | 0                    | 0   | 6      |  |

| 0              | 1     | 0                    | 1   | 2      |  |

| 1              | 1     | - 1                  | 1 1 | 7      |  |

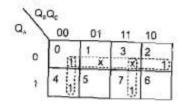

### K-map simplification for Din

$$D_{m} = \overline{Q}_{A} + \overline{Q}_{B}\overline{Q}_{C} + Q_{B}Q_{C}$$

$$= \overline{Q}_{A} + Q_{B} = Q_{C}$$

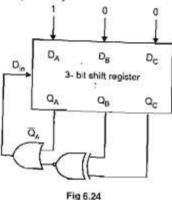

The logic diagram is shown in Fig.6.24. The initial state is 100. So the input for  $D_A$ ,  $D_B$  and  $D_C$  are 100 respectively.

# 6.8 Sequence Detector

A sequence detector is a sequential logic circuit that can be used to detect whether a given sequence of bits has been received or not. We can draw the state diagram when we know the sequence and then follow the steps to design sequential logic circuit to obtain the sequence detector sequential logic circuit.

Generally sequence detector produces an output = 1, whenever it detects the desired input sequence and '0' for other cases. There are two types of detectors:

- 1. A detector which detects overlapping input sequence, and

- 2. A detector which detects non-overlappling input sequence.

Example 6.11 Design a sequence detector which detects the sequence (00011.

#### □ Solution

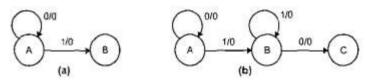

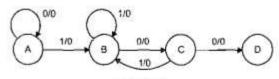

In general, the number of states in the state diagram is equal to the number of bits in the sequence. Once the number of states is known, one has to draw the directed lines with inputs and outputs as weighed between the two states. Let us start to draw state diagram, assuming initial state is A.

State A: In this state, the detector may receive either an input 0 or 1. Based on these inputs, a sequence detector is either in same state or move on to the next state as shown in Fig. 6.26.

When input is 1, we have detected first bit in the sequence, hence we have to go to next state (B) to detect the next bit in the sequence

Fig 6.26

When input is 0, we have to remain in state A, because bit '0' is not the first bit in the sequence

State B: When input is 0, we have detected the second bit in the sequence. Hence we have to go to Next state (C) to detect the next bit in the sequence [See Fig.6.26(b)]

When input is 1, we have to remain in the state B, because 1 which we have detected may start the sequence output which is still zero for both cases

State C: When input is 0, we have detected the third bit in the sequence, hence we have to go next state (D) to detect the next bit in the sequence

Fig 6.26(c)

When input is 1, we have to go to state B, because 1 which we have detected may not be in the sequence to be detected but it may be the start/bit of the sequence, hence we can move to state B. The output is still zero (See Fig.6.26(c))

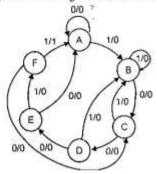

State D to State F: As explained for state A, state B and state C, if the desired bit is detected, we have to go for the next state otherwise we have to go to the previous state from where we can continue the desired sequence. When complete sequence is detected, we have to make output 1 and go to the initial state. The complete state diagram is shown in Fig.6.26(d).

Fig 6.26(d)

#### State assignment

Assume that for state assignment, we need 3 flip flops to construct the sequence detector circuit. The sequence detector has a total of 6 states. Two flip flops are enough for less than or equal to 4 states. Hence  $3(2^3 = 8)$  flip flops are required to construct the sequence detector. We choose JK flip flop and the flip flops are labeled as A.B and C, assuming state assignments as A = 000.B =001.C = 010.D = 011.E = 100 and F = 101.

Excitation table

We can easily write the excitation table from the state diagram.

| Input | Pre | esent | state |           | vext stat | e         | Output |       | F              | ip flo | ր Լորւ | its |     |

|-------|-----|-------|-------|-----------|-----------|-----------|--------|-------|----------------|--------|--------|-----|-----|

| X     | A   | B     | C     | $A_{n+1}$ | $B_{n+1}$ | $C_{n+1}$ | Y      | $J_A$ | K <sub>4</sub> | Jg     | KH     | Jc. | Kc  |

| 0     | 0   | 0     | 0     | 0         | 0         | 0         | 0      | 0     | X              | 0      | X      | 0   | X   |

| 0     | 0   | 0     | 1     | 0         | . L       | 0         | 0      | 0     | X              | 1      | X      | X   | 1   |

| 0     | 0   | 11    | 0     | 0         | 1         | I I       | 0      | 0     | X              | X      | 0      | 1   | X   |

| ()    | 0   | 1     | 1     | - 1       | 0         | 0         | 0      | 1     | X              | X      | 1      | N   | 1   |

| 1)    | 1   | 0     | 0     | 0         | 0         | 0         | - 0    | X     | 1              | 0      | X      | 0   | X   |

| ()    | 1   | 0     | 1     | 3         | 1         | 0         | 0      | X     | 1              | 1      | X      | X   | 1   |

| 1     | 0   | 0     | 0     | .0        | 0         | 1         | 0      | 0     | X              | 0      | X      | 1   | X   |

| 1     | 0   | 0     | 1     | - 0       | 0         |           | 0      | 0     | X              | -0     | X      | X   | 0   |

| 1     | 0   | 13    | 0     | 0         | : 0       | T         | 0      | 0     | X              | X      | T      | 1   | X   |

| 10.   | 0   | 1     | -1    | -0        | 0         | -1        | 0      | 0     | X              | X      | 1      | X   | 0   |

| 1     | 1   | 0     | 0     |           | O         | - 1       | 0      | X     | 0              | ()     | X      | 1   | X   |

| - 1   | 1   | 0     | 1     | 0         | 0         | T         |        | X     | 1              | 0      | X      | X   | - 1 |

### K-map simplification

Expression for flip flop input JA

| 00 | 00      | 1       | 3 (1)   | 2    |

|----|---------|---------|---------|------|

| 01 | 4 ×     | 5<br>X  | 7 x     | 6 x  |

| 11 | 12<br>X | 13<br>X | 15<br>X | 14 x |

| 10 | 6       | 9       | 11      | 10   |

Expression for the floe input Ja

Expression for flip flop input JC

Jc= X+B

| 00 | 00    | 01   | 11   | 10 |

|----|-------|------|------|----|

| 00 | ×     | x    | ×    | ×  |

| 01 | 1     | 1    | ×    | x  |

| 11 | S0226 | 1    | ×    |    |

| 10 | ×     | i.x. | .x.) | ×  |

Expression for flip flop input K.

Expression for flip flop input Kg

Expression for flip top input Kc

Expression for Output Y

#### Logie diagram for sequence detector

Fig 6.27 Logic diagram for sequence detector

Example 6.12 Design a sequence detector to detect the sequence 101 from 10101.

#### Solution

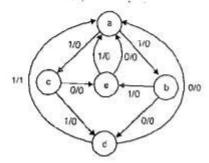

We have only 3 states because we have to detect the sequence 101 from the given number 10101. This circuit is allowed repetition.

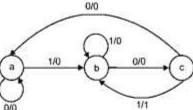

Initially, we assume that the circuit is in its reset state, state a. With a 1 coming in as first bit in the valid sequence, it will go from state a to state b with an output as 0 because we have not yet detected all the bits in the sequence. When input is 0, we detect second valid bit in the sequence so it will go from state b to state c, otherwise state b remains same. When the input is 1, we detect third bit in the sequence, which will go from state c to state b with the output as 1 because we are yet to detect all bits in the sequence. If the input is 0, it will go from state c to state a with output 0.

Fig 6.28 State diagram

The binary values are assigned to state u, h and c. Only two flip flops are enough  $(2^2 = 4)$ to design the sequence detector sequential logic circuit, by using T flip flops.

Assume the state assignment

$$a = 00,$$

$b = 01,$   $c = 10$

## Consider the input is X and the output is Y.

| Input | Pres | ent state | Next | state            | Flip f | lop Inputs | Output |

|-------|------|-----------|------|------------------|--------|------------|--------|

| X     | a I  | b         | 0,11 | b <sub>n-1</sub> | Ta     | $T_b$      | ),     |

| 0     | 0    | 0         | 0    | 0                | 0      | 0          | 0      |

| 0     | 0    | 1         | 1    | 0                | 1 1    | 1          | 0      |

| 0     | 71   | 0         | 0    | 0                | I      | 00         | - 11   |

| 0     | 11   | 1         | X    | X                | X      | X          | X      |

| 1     | 0    | 0         | 0    | 1                | 0      | 1          | - 0    |

| 1     | i i  | T -       | 11   | 1                | 0      | 0          | 1 0    |

| 11    | T    | ñ-        | 0    | 1                | 1      | 1          | 1 1    |

| T     | 11:  |           | X    | 1 N              | X      | X          | 1 N    |

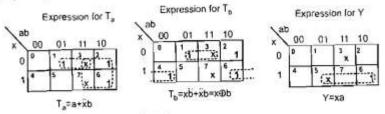

#### K-map simplification

#### Logic diagram for sequence detector

Fig 6.29 Logic diagram for sequence detector

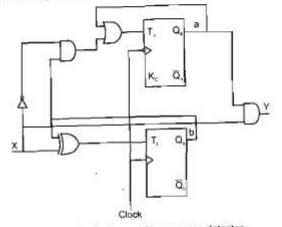

**Example 6.13** A sequential circuit with two D flip flops A and B and input Xand output Y is specified by the following next state and output equations

#### Digital Electronics

$$A(t+I) = AX + BX$$

$$B(t+I) = A'X$$

$$Y = (A+B)X'$$

- (a) Draw the logic diagram of the circuit

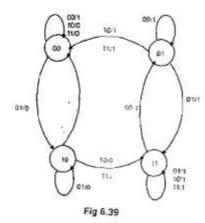

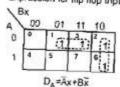

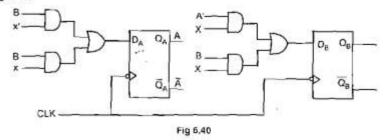

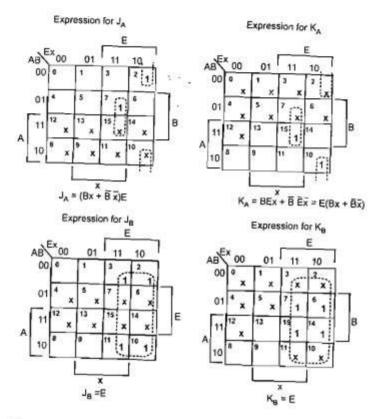

- (b) Derive the state table